TSMC, le plus grand fabricant de puces au monde, a commencé la production de masse de processeurs avec la technique Wafer-on-Wafer (WoW) : L’entreprise britannique Graphcore l’utilise pour augmenter jusqu’à 40% les fréquences d’horloge de son processeur d’intelligence artificielle Colossus de 826 mm², et donc ses performances.

Le processeur d’intelligence artificielle proprement dit reste en grande partie identique, avec 1472 cœurs d’unité de traitement de l’intelligence et 900 Mo de mémoire cache SRAM – TSMC continue de le fabriquer avec des structures de 7 nanomètres. Avant que les différents processeurs ne soient découpés dans la plaquette de silicium, TSMC ajoute une deuxième plaquette avec des structures plus grossières par-dessus.

Cette deuxième plaquette de silicium ne contient pas de transistors actifs, mais d’innombrables condensateurs dits « Deep Trench » (DTC) qui, en tant qu’accumulateurs de charge, sont placés le plus près possible des noyaux IPU et lissent l’alimentation électrique. Ils suivent pratiquement plus vite que les convertisseurs de tension sur la carte mère.

Sommaire

Plus de cadence, plus d’efficacité

La fréquence d’horloge des cœurs IPU passe ainsi de près de 1,35 à un peu plus de 1,85 GHz, avec une augmentation simultanée de l’efficacité de 9 à 16 pour cent selon le modèle d’entraînement. L’augmentation de l’efficacité est particulièrement remarquable, car la fréquence d’horloge supplémentaire se répercute habituellement de manière quadratique sur la courbe de tension. La consommation électrique du nouveau processeur Colossus de Graphcore augmente certes, mais de manière moins que proportionnelle à l’augmentation de la fréquence.

De manière analogue à l’horloge du cœur, la SRAM intégrée fonctionne également plus rapidement, de sorte que le taux de transfert au sein d’un processeur passe à 65 TByte/s. En revanche, la communication entre les différents processeurs d’une carte mère reste à 320 Go/s avec 10 liens IPU.

Bow-IPU avec wafers empilés (3 images)

Sœur technique de la mémoire cache empilée d’AMD

La technique Wafer-on-Wafer ressemble beaucoup au procédé Chip-on-Wafer (CoW) qu’AMD utilise sur le Ryzen 7 5800X3D pour poser un cache-dièse supplémentaire. Cependant, avec WoW, TSMC ne place pas des puces déjà découpées sur les processeurs, mais découpe les puces finales à partir de deux wafers reliés entre eux. Chez AMD, ce serait un gaspillage de silicium, car le cache-die ne couvre pas la totalité des chipsets de calcul.

Avec Graphcore, en revanche, WoW a des avantages techniques : Comme deux wafers peuvent être alignés en filigrane l’un sur l’autre plus qu’une seule puce sur un wafer, TSMC peut concevoir des trous métallisés (TSV) plus étroits entre les deux couches de silicium et ainsi loger plus de TSV sur la même surface de puce.

De plus, TSMC peut amincir davantage le deuxième wafer avec les condensateurs Deep Trench après la mise en place, car le wafer de base avec les processeurs Colossus stabilise la construction. TSMC commence donc par placer les deux wafers l’un sur l’autre, insère les trous d’interconnexion, ponce le wafer supplémentaire et découpe ensuite seulement les processeurs finis. Tout comme la technique CoW, WoW n’a pas besoin de points de soudure ou de micro-bosses.

Les processeurs Graphcore montrent une autre possibilité pour les concepteurs de puces d’accélérer leurs CPU, GPU et autres processeurs. AMD, Intel et Nvidia pourraient également utiliser cette technologie à l’avenir – tous trois sont clients de TSMC.

Jusqu’à 1024 processeurs d’intelligence artificielle dans un seul système

L’augmentation de la vitesse est suffisamment importante pour que Graphcore lance une nouvelle génération de produits avec la technologie WoW, sous le nom de code Bow. La plus petite configuration Bow Pod 16, avec une puissance de calcul en précision mixte de 5,6 pétaflops d’IA, utilise quatre tiroirs 1U avec chacun quatre processeurs d’IA et un tiroir 1U supplémentaire comme serveur CPU pour la gestion. Le tout s’étend jusqu’au Bow Pod 1024 composé de 16 baies de serveurs avec 358,4 pétaflops d’IA. Les Bow Pods doivent pouvoir entraîner toutes sortes de modèles d’IA plus rapidement que les serveurs DGX-A100 de Nvidia avec des accélérateurs Ampere.

Benchmarks des constructeurs sur les processeurs d’IA Bow (5 images)

Les systèmes sont déjà en cours de production en série et seront vendus à des partenaires à des prix identiques à ceux de leurs prédécesseurs. Graphcore affirme pouvoir réduire les coûts de production grâce à un volume de production plus élevé.

Perspectives de l’exascale

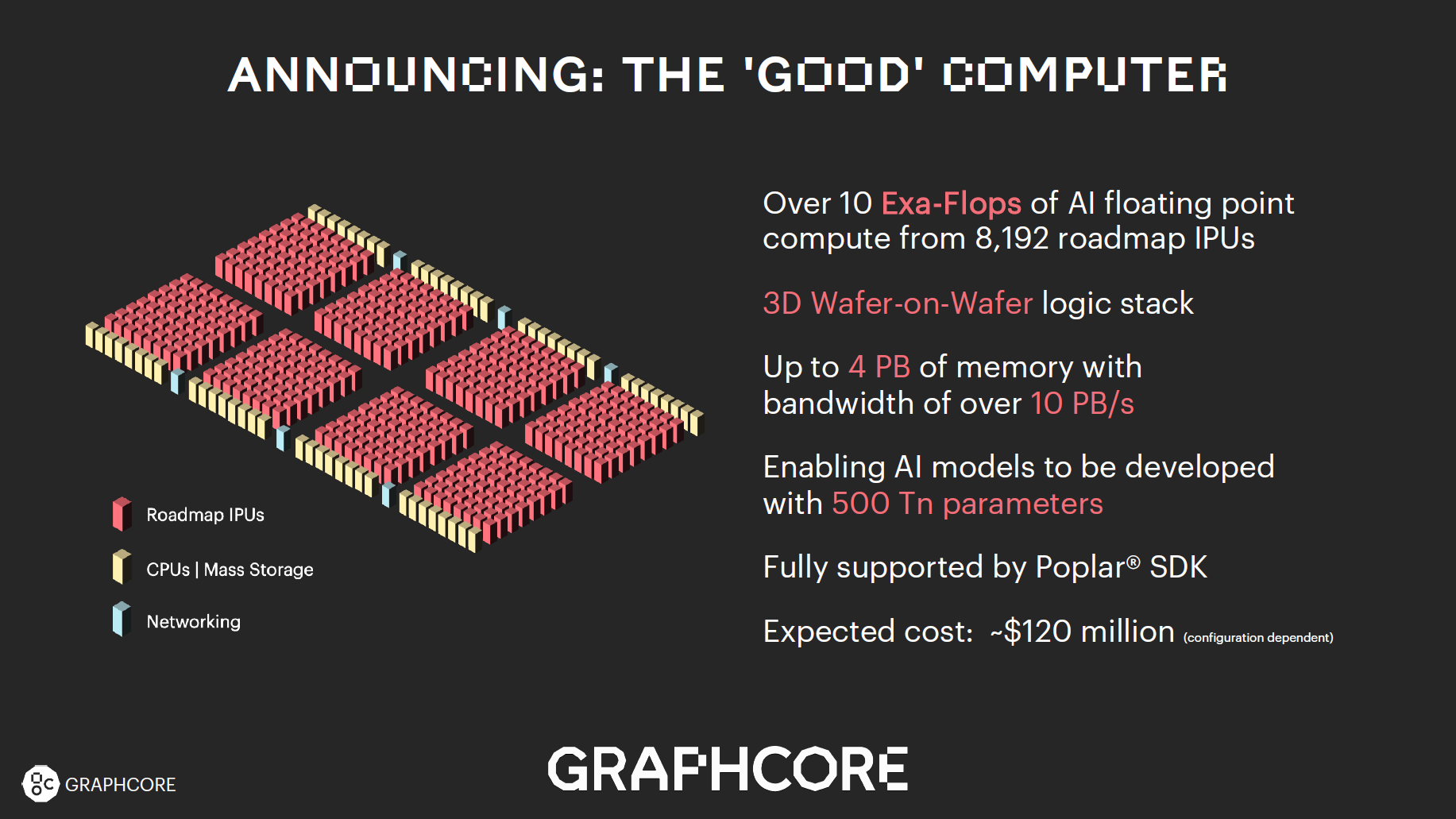

La génération Bow permet de combler le temps d’attente jusqu’au véritable prochain processeur Graphcore, dont la sortie est prévue pour 2024. L’entreprise veut lancer sur cette base le superordinateur d’intelligence artificielle « The Good Computer » avec une puissance de calcul d’au moins 10 ExaFlops. Les clients fortunés devraient pouvoir acquérir ce système pour 120 millions de dollars US.

(Image : Graphcore)