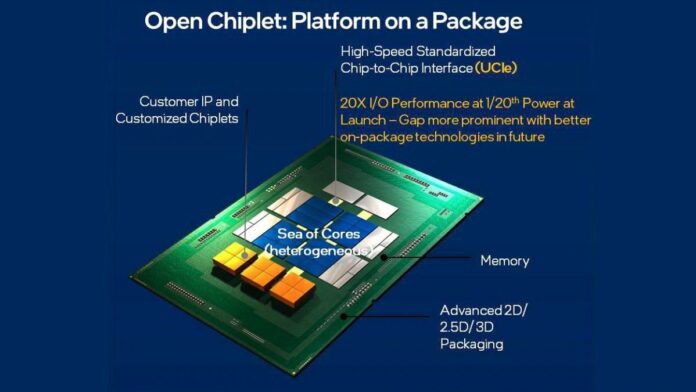

Un comité industriel avec la participation des plus grands fabricants de puces a adopté la norme « Universal Chiplet Interconnect Express » (UCIe). Elle doit permettre aux développeurs de puces d’assembler plus facilement des processeurs et des accélérateurs de calcul à partir de plusieurs puces de différents fournisseurs, qui fonctionnent ensemble dans un boîtier (package). UCIe est étroitement lié à PCI Express (PCIe) et au Compute Express Link (CXL) qui en découle pour la communication cohérente avec la mémoire cache.

Avec UCIe, il devient plus facile de placer par exemple un chiplet de CPU avec des noyaux ARM avec un chiplet de GPU avec la technologie AMD ainsi qu’un FPGA Intel dans un boîtier commun. Cela pourrait être intéressant pour les exploitants de grands centres de calcul qui développent (ou font développer) leurs propres processeurs spéciaux.

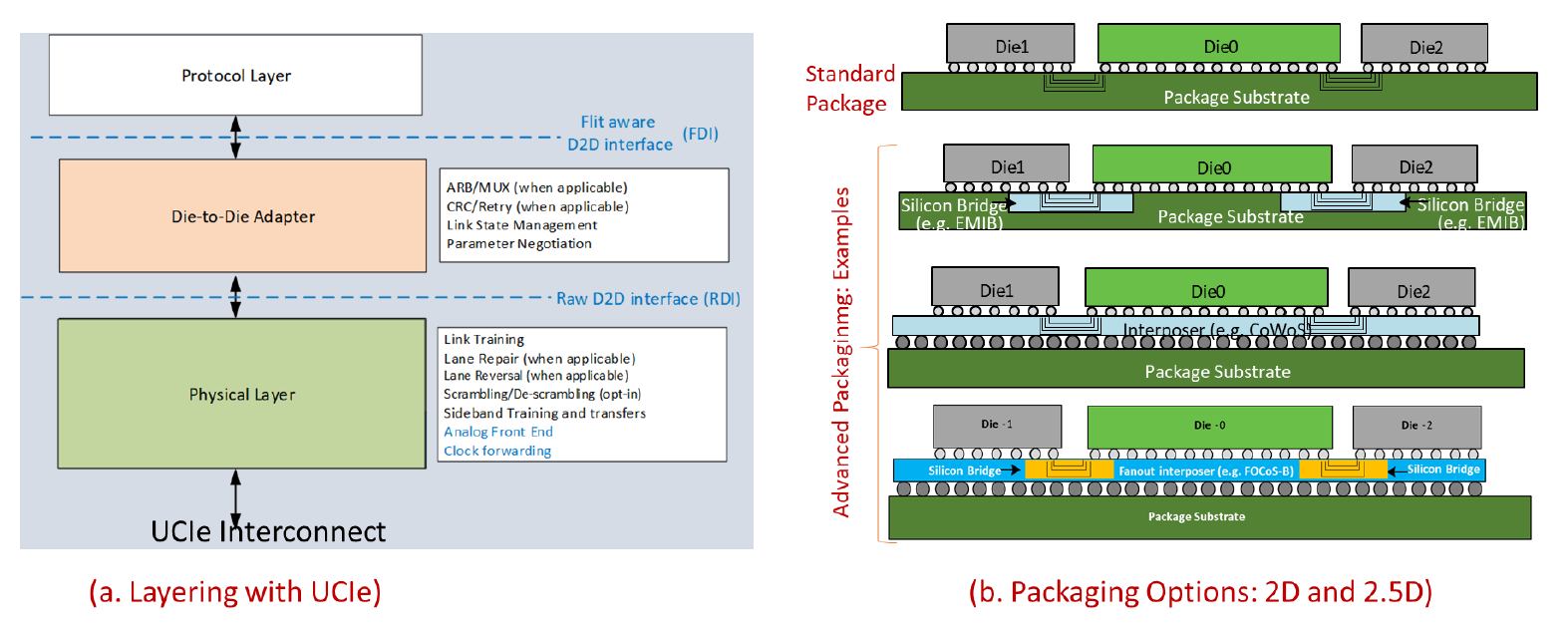

UCIe propose certes une interface standard performante pour le couplage chiplet-chiplet, mais laisse (par la force des choses) de nombreuses questions en suspens : Par exemple, la compatibilité mécanique et thermique des puces entre elles et avec le matériau de support. Pour le couplage « électromécanique » pratique des puces ou des carreaux (tiles), il existe en outre de nombreux procédés concurrents et brevetés de différentes entreprises : Par exemple l’EMIB et Foveros d’Intel ainsi que Integrated Fan-Out (InFO) et CoWoS de TSMC ou encore Fan-Out Chip on Substrate (FOCoS) du plus grand prestataire de services OSAT du monde, ASE (OSAT : Outsourced Semiconductor Assembly Test).

(Image : UCIe)

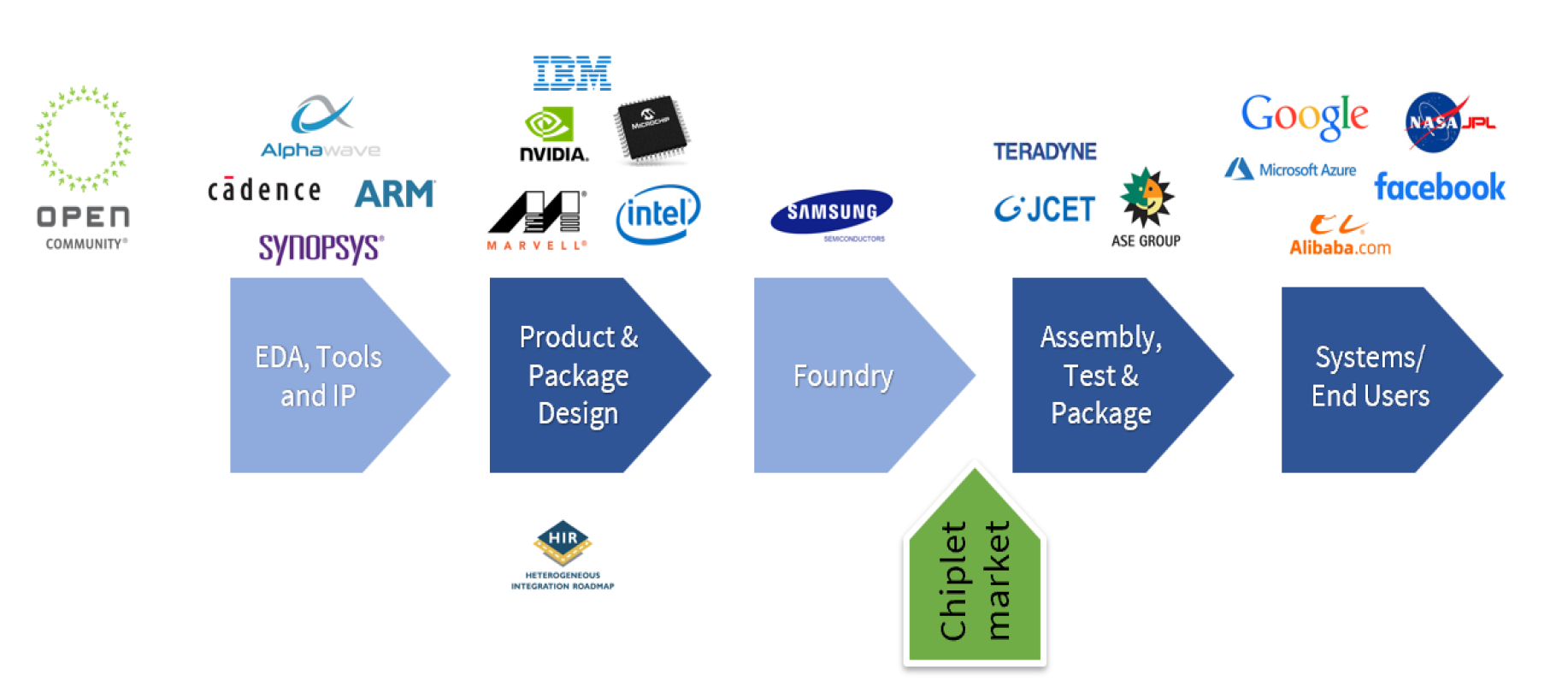

Les partenaires de coopération de l’UCIe, AMD, Intel, Arm, Qualcomm, Samsung, TSMC et ASE, ainsi que les exploitants de centres de données hyperscale Google Cloud, Meta (Facebook) et Microsoft, souhaitent également coopérer à l’avenir sur d’autres spécifications pour un écosystème de puces ouvert. Il s’agira entre autres de standardiser les formes de construction et les fonctions de gestion.

Autres initiatives en matière de chiplet

Dans le cadre de l’Open Compute Project (OCP) initié par Meta/Facebook, auquel participent également depuis longtemps Microsoft, Google Cloud, AMD, Arm, Intel et Samsung, le « groupe chiplet » Open Domain-Specific Architetcture (ODSA) travaille. Celui-ci veut mettre sur pied un marché ouvert de chiplets.

(Image : OCP-ODSA)

Les fabricants de logiciels de développement de puces (EDA, Electronic Design Automation) comme Cadence et Synopsys collaborent également au projet ODSA.