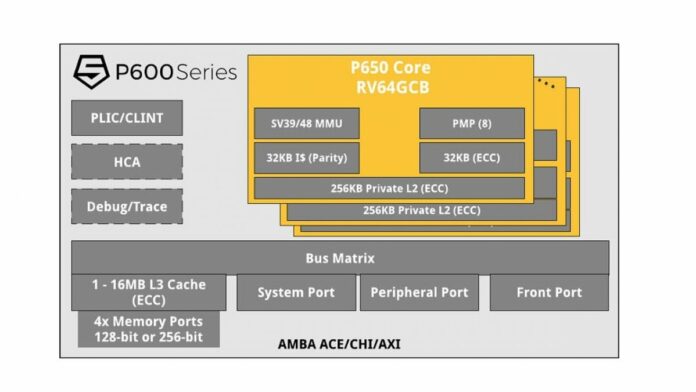

Selon le développeur SiFive, le Performance P650 est le noyau de processeur le plus puissant à ce jour avec l’architecture de jeu d’instructions RISC-V divulguée. Il pourrait être utilisé d’ici un à deux ans dans des processeurs compatibles avec Linux, avec jusqu’à 16 cœurs de CPU, 16 Mo de cache L3 et de nombreux canaux de mémoire. Chaque cœur dispose de 64 Ko de mémoire cache L1 (32 pour les données et 32 pour les instructions) et de 256 Ko de mémoire cache L2. La puissance de calcul par cycle devrait être comparable à celle de l’ARM Cortex-A77 annoncé en 2019.

SiFive voit des domaines d’application pour les SoC avec des noyaux P650, entre autres dans les serveurs, les véhicules et les appareils mobiles. Le SiFive Performance P650 est conforme à la spécification RISC-V RV64GCB ainsi qu’aux nouvelles spécifications pour l’hyperviseur et la virtualisation adoptées par la RISC-V Foundation.

Sommaire

15 nouvelles spécifications RISC-V

Quelques jours avant le sommet RISC-V à San Francisco, les membres de la fondation RISC-V ont ratifié 15 spécifications qui décrivent au total 40 extensions de la RISC-V-ISA. Parmi celles-ci, on trouve des fonctions de virtualisation, mais aussi des commandes vectorielles et des fonctions de cryptographie scalaire. Les versions actuelles des spécifications RISC-V sont disponibles sur GitHub.

Travail en cours

Tout comme SiFive, l’entreprise Rivos, qui travaille encore en mode furtif, est située dans la Silicon Valley, à proximité du siège d’Intel à Santa Clara. Quelques experts en CPU de haut niveau, qui ont déjà travaillé pour des entreprises comme PA Semi, y travaillent probablement sur une puce RISC-V pour serveurs. Rivos est déjà membre de la RISC-V-Foundation et s’est assuré le PCI-ID 7933 (0x1EFD).

A d’autres endroits, les maladies d’enfance de la technique RISC-V sont visibles. Ainsi, le SoC RISC-V StarFive JH7100 nécessite des patchs Linux spéciaux pour les accès DMA des contrôleurs E/S, car la puce n’assure pas elle-même la cohérence de la mémoire cache. Des restrictions similaires s’appliquent à l’Allwinner D1 avec le noyau RV64GC XuanTie C906.

- Podcast Bit-Rauschen sur le thème RISC-V :